Novinka:ST: STM32H743 - brutálny výkon s Cortex-M7

(Kategória: Semiconductor-ZONE)

Zaslal wek

21.10.2016-08:05

Väčšina čitateľov uzone si zrejme už všimla, že ST oznámilo nový rad mcu s jadrom ARM Cortex-M7 pod označením STM32H7, a jeho prvý člen, STM32H743. Písmeno H v označení nepochybne znamená "high-speed" a poukazuje na neobvykle vysoký hodinový takt procesorového jadra 400MHz.

Týmto ST prevzalo vedenie v pretekoch o najvyšší výkon v "klasických" mcu. Doterajšie prvenstvo - ako sme Vás už informovali - patrilo Atmelu (dnes už súčasť Microchipu) s radom SAMV7x, ktorého Cortex-M7 jadro beží na 300MHz.

Vlastnosti

Podľa ST, s frekvenciou jadra 400MHz STM32H473 dosiahol EEMBC® CoreMark® skóre 2010. Skóre prepočítané na 1MHz je tak 5.01, čo je navlas rovnaké ako hodnota pre staršie STM32F7 či konkurenčný SAMV7x. Nečudo - jedná sa o rovnaké jadro, CoreMark benchmark je dostatočne malý a jednoduchý aby sa zmestil do L1 cache; a už vôbec nie je určený na to, aby postihol rozdiely v architektúre zberníc, prípadne v perifériách. Toto čitatelia uzone samozrejme vedia, a tešia sa na to, ako rozmeníme tieto hodnoty na drobné. Bohužiaľ, zatiaľ zverejnené údaje nedovoľujú posúdiť ani len to, či sa uvedená maximálna frekvencia dá bez čakacích cyklov využiť aj pri behu mimo L1 cache, menovite z ITCM SRAM. Podľa blokového zapojenia, na rozdiel od STM32F7 už FLASH nie je pripojená alternatívne cez TCM zbernicu a ART akcelerátor, ale len cez AXI zbernicovú maticu, takže sa zdá, že jedinou akceleráciou pri behu z FLASH je štandardný mechanizmus L1 cache.

Obvod STM32H743 má však ešte jednu pozoruhodnú vlastnosť, a to je celkový objem SRAM - je jej až 1MB (plus 16+16kB L1 Cache, ktoré sa do celkovej užívateľom použiteľnej SRAM nemajú počítať, lebo sú súčasťou jadra a cachujú aj užívateľskú SRAM), rozdelená medzi ITCM, DTCM, niekoľko blokov užívateľskej SRAM (jeden alebo viac blokov na každej zbernicovej matici - pozri v ďalšom) a (baterkou) zálohovanej SRAM. FLASH je až 2MB a má už aj ECC bity (redundantné bity na kontrolu a opravu chýb).

Mix periférií nepriniesol nič prevratné, v podstate sa jedná o už zabehnuté periférie, aj keď v mohutnej zostave. Pri takomto silnom modeli pochopiteľne nechýba podpora Ethernetu a grafiky (rozhranie pre kameru, LCD kontrolér, JPEG codec).

Čip je vyrábaný 40nm technológiou.

U takto výkonného obvodu spotreba nebýva na prvom mieste. Tlačová správa uvádza "less than 280uA/MHz in run mode" čo predstavuje vyše 100mA pri 400MHz. To síce nie je ani pri 3V až tak veľa, ale s najväčšou pravdepodobnosťou sa jedná o "reklamný" údaj zahrňujúci len beh samotného jadra a pri takto rozsiahlych perifériách to bude v praxi viac. Aj vzhlľadom na 3 interné napájania (ktoré je pochopiteľne potrebné externe filtrovať, + zálohové napätie s vlastným LDO na 0.9V) nebude korektné riešenie najmä zemnenia, samotného napájania a ani chladenia úplne triviálne...

Nudný zoznam vllastností

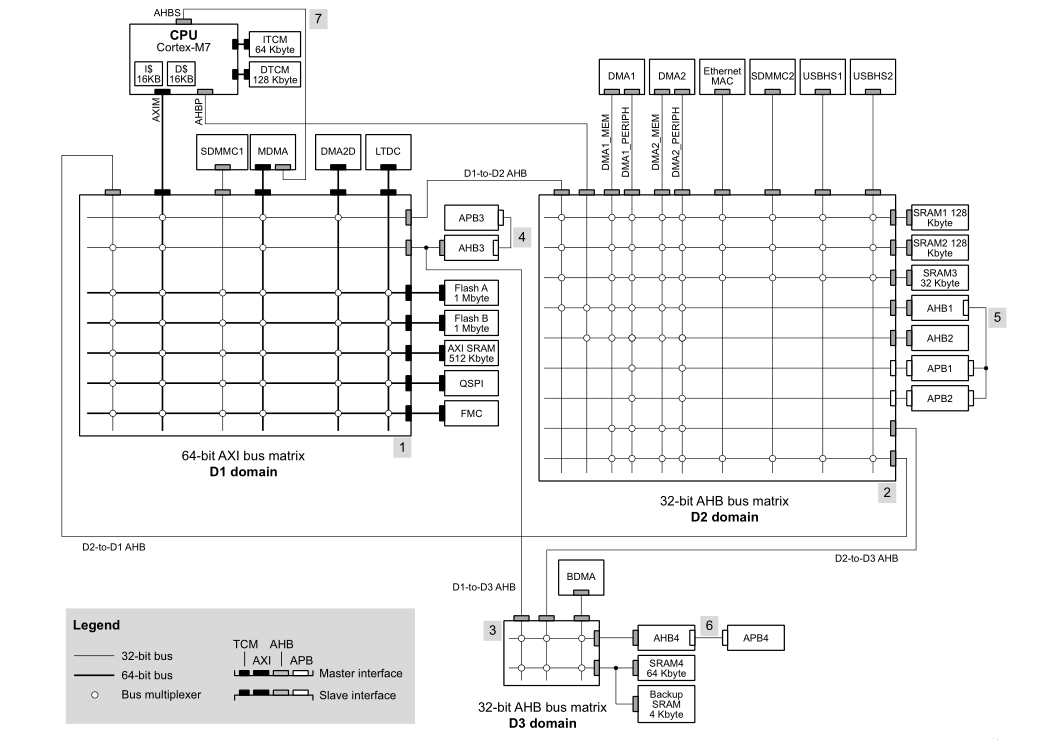

Blokové zapojenie

Tak toto je masaker (klik pre zväčšenie).

Ako je z tejto schémy zberníc vidieť, obvod obsahuje tri zbernicové matice (pripojenie jednotlivých periférií na zbernice je znázornené na blokovom zapojení na obr. 1 v databriefe; tento je však príliš veľký aby sme ho tu uvádzali, záujemca si určite rád databrief stiahne a prezrie sám ). Každá matica súčasne predstavuje aj samostatnú napájaciu doménu (označené D1 až D3), pričom periférie aj mastre sú maticiam priradené podľa výkonnosti.

). Každá matica súčasne predstavuje aj samostatnú napájaciu doménu (označené D1 až D3), pričom periférie aj mastre sú maticiam priradené podľa výkonnosti.

Matica v doméne D1 je najvýkonnejšia a je to 64-bitová AXI matica (aj keď nie všetky pripojené zbernice sú 64-bitové); zvyšné dve matice sú 32-bitové. Toto je zo systémového pohľadu zásadný rozdiel oproti radu STM32F7, kde jediná matica je 32-bitová, a 64-bitové rozhranie procesoru AXIM má pripojenú zvláštnu "prevodnú" jednotku na niekoľko 32-bitových AHB zberníc zapojených do matice, plus jednu 64-bitovú "skratku" priamo k FLASH. 64-bitová matica v STM32H7 umožňuje najmä procesoru (ale aj iným mastrom) pristupovať do pamätí pripojených na túto maticu (FLASH a väčina užívateľskej pamäti) 64-bitovo.

Na AXI maticu je ako master pripojený predovšetkým samotný procesor, ďalej 16-kanálová výkonná DMA jednotka MDMA, SD/MMC jednotka SDMMC1, grafický akcelerátor DMA2D a LCD kontrolér LTDC; a ako zvláštny master je "spätný" prepoj D2-to-D1 (cez ktorý mastre matice D2 môžu čítať/zapisovať slave v matici D1). Slave sú tu predovšetkým pamäte (s 64-bitovým prístupom) - 2 banky FLASH, 512kByte SRAM, jednotky externých pamätí. Zvyšné dva slave predstavujú prepoje na matice D1-to-D2 a D1-to-D3, pričom k tej druhej je pripojených ešte niekoľko "lokálnych" periférií cez AHB3/APB3 (napr. "strana registrov" LCD kontroléra - "strana dát" tejto jednotky je, ako bolo už uvedené, pripojená priamo do AXI matice ako master).

Matica D2 prepája väčšinu periférií a niekoľko výkonnejších mastrov (ETH, 2xUSBHS, SDMMC2) vrátane dvoch DMA kontrolérov. Do značnej miery predstavuje táto matica ekvivalent pôvodnej matice v 'F7/'F4; pripojenie procesora tu predstavuje prepoj D1-to-D2 (plus priama "skratka" zo zvláštneho periférneho portu procesora AHBP, ktorá je v matici pripojená len do dvoch slave AHB zberníc). Slave sú tri bloky SRAM, dve AHB zbernice ktoré spolu so svojimi APB zbernicami obsluhujú väčšinu periférií typu SPI/I2C/UART atď, (aj dve APB zbernice ale len ako slave pre DMA - viď v ďalšom - všetky ostatné mastre k APB pristupujú len cez príslušné AHB) a "prepoje" - už spomenutý D2-to-D1 a D2-to-D3. Je vhodné si tu všimnúť DMA kontroléry. Majú po 8 kanálov a 2 porty smerom k matici, rovnako ako DMA jednotky v 'F7/'F4; na rozdiel od nich však jeden z portov (periférny) nie je priamo prepojený "skratkou" na príslušnú APB zbernicu, ale je vedený tiež maticou, s prístupom na všetky slave (vrátane oboch APB, ako bolo spomenuté). Ďalším rozdielom je "request router", v ktorom by malo byť možné voľnejšie presmerovávať požiadavky na prenos od jednotlivých periférií na jednotlivé kanály DMA (presné informácie zatiaľ chýbajú). Obe tieto zmeny prispievajú k vyššej flexibilite použitia DMA jednotiek (ktorá v 'F7/'F4 naráža na množstvo "natvrdo zapojených" obmedzení), zjavne za cenu väčšieho počtu tranzistorov a prepojov.

Matica D3 je nízkopríkonová a má okrem prepojov z D1 a D2 jediný samostatný master a to je "Basic" DMA (BDMA) jednotku. Ako slave má blok 64kB SRAM a 4kB zálohovanej SRAM, a AHB4 zbernicu ktorá spolu s APB4 zbernicou obsluhuje periférie ako RTC, low- power timery, LPUSART a iné.

"Prepoje" sú teda obojsmerné medzi všetkými tromi maticami s výnimkou smeru D3-to-Dx, takže jediný D3 master BDMA môže pristupovať len na slave v D3. Treba si pritom uvedomiť, že tieto "prepoje" (AHB zbernice) sú "pomalšie" - väčšina z nich môže ísť max. do rýchlosti 200MHz. Samozrejme, v každej matici nastáva proces arbitrácie medzi mastrami, ktorý vnáša latencie do prístupu k pripojeným slave aj keď nenastáva konflikt. Ak je z nejakého mastra pristupovaná periféria pripojená na inú zbernicu ktorá je slavom inej matice než v ktorej sa nachádza master, tento prístup prechádza oboma maticami plus prepojom medzi nimi, takže predstavuje určité spomalenie a záťaž pre všetky dotknuté zbernice a matice. Preto napríklad nie je vhodné, aby jednotka DMA1 (master v D2) zbytočne pristupovala na externú pamäť (trebárs SRAM) cez FMC (čo je slave v D1) - znamenalo by to cestu cez D2, prepoj D2-D1, a cestu cez D1; je vhodnejšie, ak si DMA1 rieši väčšinu pamäťových potrieb niektorou z lokálnych pamätí v D2, t.j. SRAM1-SRAM3.

Na takto hierarchicky zostavený obvod je teda vhodné nazerať ako na výkonný procesor s úzko pripojenými pamäťami (to predstavuje D1), a k nemu voľnejšie pripojenú sadu periférií (D2 a D3). Očakáva sa, že D1 rieši výpočtovo náročné úlohy (number crunching), kým väčšina riadiacich hard-real-time úloh sú riešené buď priamo perifériami (ktoré každá sama osebe predstavuje systém nemalej zložitosti), menšia časť z nich a väčšina presunu dát je riešená DMA jednotkami, a procesor nad nimi vlastne robí len dohľad prípadne dávkovo spracováva data.

Je to ešte o jednu úroveň vzdialenejšie modelu, ktorý zaviedli 8-bitové mcu. Tie mali všetky zdroje - procesorové jadro, pamäte aj periférie - úzko zviazané a prísne synchrónne, čo umožňovalo vývojárovi mať veľmi presnú kontrolu nad časovaním; na druhej strane výpočtový výkon bol častokrát nedostatočný pre náročnejšie aplikácie. 32-bitové mcu - vlastne SoC - priniesli o rád vyšší výpočtový výkon; na výmenu za to sú však jednotlivé moduly zviazané voľnejšie cez sústavu zberníc a signálov, niekedy aj v rôznych časovacích doménach, kde dosiahnutie presného časovania procesov riadených priamo z procesora je obtiažne ba až nemožné. STM32H7 posúva tento rozpor ešte o stupeň ďalej.

Cena, dostupnosť

Jedná sa samozrejme o predbežné oznámenie, a obvody STM32H743 existujú ešte len ako vzorky, preto o cene a dostupnosti sa zatiaľ nedá hovoriť. Tlačová správa uvádza, že obvod bude vyrábaný v Q2 2017, a predbežná cena najnižšieho modelu s 1MB FLASH v 100-pinovom puzdre je $8.17 pri 10k.

Z doterajších skúseností je pravdepodobné, že niekedy v druhej polovici budúceho roku sa objavia prvé kusy samotného obvodu ako aj podporné kity typu DISCOVERY či Nucleo a maloobchodná cena v bude pravdepodobne bližšie k $20. Pri takto zložitom obvode však treba rátať aj s obdobím počiatočných potiaží v zvládnutí softwaru a určitým množstvom errat, ako to k tak príšerne zložitým obvodom nevyhnutne patrí.

Odkazy

Táto novinka je z mikroZONE

( http://www.mikrozone.sk/news.php?extend.1203 )

(Kategória: Semiconductor-ZONE)

Zaslal wek

21.10.2016-08:05

Väčšina čitateľov uzone si zrejme už všimla, že ST oznámilo nový rad mcu s jadrom ARM Cortex-M7 pod označením STM32H7, a jeho prvý člen, STM32H743. Písmeno H v označení nepochybne znamená "high-speed" a poukazuje na neobvykle vysoký hodinový takt procesorového jadra 400MHz.

Týmto ST prevzalo vedenie v pretekoch o najvyšší výkon v "klasických" mcu. Doterajšie prvenstvo - ako sme Vás už informovali - patrilo Atmelu (dnes už súčasť Microchipu) s radom SAMV7x, ktorého Cortex-M7 jadro beží na 300MHz.

Vlastnosti

Podľa ST, s frekvenciou jadra 400MHz STM32H473 dosiahol EEMBC® CoreMark® skóre 2010. Skóre prepočítané na 1MHz je tak 5.01, čo je navlas rovnaké ako hodnota pre staršie STM32F7 či konkurenčný SAMV7x. Nečudo - jedná sa o rovnaké jadro, CoreMark benchmark je dostatočne malý a jednoduchý aby sa zmestil do L1 cache; a už vôbec nie je určený na to, aby postihol rozdiely v architektúre zberníc, prípadne v perifériách. Toto čitatelia uzone samozrejme vedia, a tešia sa na to, ako rozmeníme tieto hodnoty na drobné. Bohužiaľ, zatiaľ zverejnené údaje nedovoľujú posúdiť ani len to, či sa uvedená maximálna frekvencia dá bez čakacích cyklov využiť aj pri behu mimo L1 cache, menovite z ITCM SRAM. Podľa blokového zapojenia, na rozdiel od STM32F7 už FLASH nie je pripojená alternatívne cez TCM zbernicu a ART akcelerátor, ale len cez AXI zbernicovú maticu, takže sa zdá, že jedinou akceleráciou pri behu z FLASH je štandardný mechanizmus L1 cache.

Obvod STM32H743 má však ešte jednu pozoruhodnú vlastnosť, a to je celkový objem SRAM - je jej až 1MB (plus 16+16kB L1 Cache, ktoré sa do celkovej užívateľom použiteľnej SRAM nemajú počítať, lebo sú súčasťou jadra a cachujú aj užívateľskú SRAM), rozdelená medzi ITCM, DTCM, niekoľko blokov užívateľskej SRAM (jeden alebo viac blokov na každej zbernicovej matici - pozri v ďalšom) a (baterkou) zálohovanej SRAM. FLASH je až 2MB a má už aj ECC bity (redundantné bity na kontrolu a opravu chýb).

Mix periférií nepriniesol nič prevratné, v podstate sa jedná o už zabehnuté periférie, aj keď v mohutnej zostave. Pri takomto silnom modeli pochopiteľne nechýba podpora Ethernetu a grafiky (rozhranie pre kameru, LCD kontrolér, JPEG codec).

Čip je vyrábaný 40nm technológiou.

U takto výkonného obvodu spotreba nebýva na prvom mieste. Tlačová správa uvádza "less than 280uA/MHz in run mode" čo predstavuje vyše 100mA pri 400MHz. To síce nie je ani pri 3V až tak veľa, ale s najväčšou pravdepodobnosťou sa jedná o "reklamný" údaj zahrňujúci len beh samotného jadra a pri takto rozsiahlych perifériách to bude v praxi viac. Aj vzhlľadom na 3 interné napájania (ktoré je pochopiteľne potrebné externe filtrovať, + zálohové napätie s vlastným LDO na 0.9V) nebude korektné riešenie najmä zemnenia, samotného napájania a ani chladenia úplne triviálne...

Nudný zoznam vllastností

- 32-bit ARM® Cortex®-M7 core, double-precision FPU, 16 KB data and 16 KB of instruction L1 cache, frequency up to 400 MHz, DSP instructions

- up to 2 MB of Flash memory, 2 banks (read while write), 256-bit wide lines + 10 ECC bits

- 1 MB of SRAM: 64 KB ITCM SRAM, 128 KB DTCM SRAM, 864 KB user SRAM, 4 KB Backup SRAM

- external memory interfaces: Dual mode Quad-SPI, external memory controller with up to 32-bit data bus: SRAM, PSRAM, SDRAM/LPSDR SDRAM, NOR/NAND memories

- 1.62 to 3.6 V application supply and I/Os, embedded scalable internal LDOs, dedicated USB power embedding a 3.3 V internal regulator to supply the internal PHYs

- POR, PDR, PVD and BOR, low power modes

- Internal oscillators: 64 MHz HSI, 48 MHz RC, 4 MHz CSI, 40 kHz LSI; external oscillators: 1-48 MHz HSE, 32.768 kHz LSE; 3x PLLs (1 for the system clock, 2 for kernel clocks) with fractional mode

- 4 DMA controllers

- 4× I2C FM+, 4× USART/4x UARTs (ISO7816 interface, LIN, IrDA, modem control) and 1× LPUART, 6× SPIs (3 with muxed duplex I2S, 1x I2S in LP domain), 4× SAIs (serial audio interface), S-PDIF RX, Digital filters for sigma delta modulator (DFSDM) with 8 channels/4 filters

- SWPMI single-wire protocol master I/F, MDIO Slave interface, 2× SD/SDIO/MMC interfaces, HDMI-CEC

- 2× CAN

- 2× USB OTG interfaces (1FS, 1HS/FS)

- Ethernet MAC interface with DMA controller

- 8- to 14-bit camera interface up to 80 MHz

- 3× ADCs with 16-bit max. resolution (14 bits 2.7 MSPS, 16 bits 168 kSPS), 1× temperature sensor

- 2× 12-bit D/A converters (1 MHz)

- 2× ultra-low- power comparators,

- 2× operational amplifiers (8 MHz bandwidth)

- LCD-TFT controller supporting up to XGA Resolution, DMA2D accelerator, Hardware JPEG Codec

- 1× high-resolution timer (2.5 ns max resolution), 2× 32-bit timers, 12× 16-bit timers, 5× 16-bit low- power timers

- RTC with sub-second accuracy and hardware calendar

- SWD & JTAG debug interfaces, 4 Kbyte Embedded Trace Buffer

- LQFP100/144/176/208, UFBGA176+25, TFBGA240+25

Blokové zapojenie

Tak toto je masaker (klik pre zväčšenie).

Ako je z tejto schémy zberníc vidieť, obvod obsahuje tri zbernicové matice (pripojenie jednotlivých periférií na zbernice je znázornené na blokovom zapojení na obr. 1 v databriefe; tento je však príliš veľký aby sme ho tu uvádzali, záujemca si určite rád databrief stiahne a prezrie sám

). Každá matica súčasne predstavuje aj samostatnú napájaciu doménu (označené D1 až D3), pričom periférie aj mastre sú maticiam priradené podľa výkonnosti.

). Každá matica súčasne predstavuje aj samostatnú napájaciu doménu (označené D1 až D3), pričom periférie aj mastre sú maticiam priradené podľa výkonnosti. Matica v doméne D1 je najvýkonnejšia a je to 64-bitová AXI matica (aj keď nie všetky pripojené zbernice sú 64-bitové); zvyšné dve matice sú 32-bitové. Toto je zo systémového pohľadu zásadný rozdiel oproti radu STM32F7, kde jediná matica je 32-bitová, a 64-bitové rozhranie procesoru AXIM má pripojenú zvláštnu "prevodnú" jednotku na niekoľko 32-bitových AHB zberníc zapojených do matice, plus jednu 64-bitovú "skratku" priamo k FLASH. 64-bitová matica v STM32H7 umožňuje najmä procesoru (ale aj iným mastrom) pristupovať do pamätí pripojených na túto maticu (FLASH a väčina užívateľskej pamäti) 64-bitovo.

Na AXI maticu je ako master pripojený predovšetkým samotný procesor, ďalej 16-kanálová výkonná DMA jednotka MDMA, SD/MMC jednotka SDMMC1, grafický akcelerátor DMA2D a LCD kontrolér LTDC; a ako zvláštny master je "spätný" prepoj D2-to-D1 (cez ktorý mastre matice D2 môžu čítať/zapisovať slave v matici D1). Slave sú tu predovšetkým pamäte (s 64-bitovým prístupom) - 2 banky FLASH, 512kByte SRAM, jednotky externých pamätí. Zvyšné dva slave predstavujú prepoje na matice D1-to-D2 a D1-to-D3, pričom k tej druhej je pripojených ešte niekoľko "lokálnych" periférií cez AHB3/APB3 (napr. "strana registrov" LCD kontroléra - "strana dát" tejto jednotky je, ako bolo už uvedené, pripojená priamo do AXI matice ako master).

Matica D2 prepája väčšinu periférií a niekoľko výkonnejších mastrov (ETH, 2xUSBHS, SDMMC2) vrátane dvoch DMA kontrolérov. Do značnej miery predstavuje táto matica ekvivalent pôvodnej matice v 'F7/'F4; pripojenie procesora tu predstavuje prepoj D1-to-D2 (plus priama "skratka" zo zvláštneho periférneho portu procesora AHBP, ktorá je v matici pripojená len do dvoch slave AHB zberníc). Slave sú tri bloky SRAM, dve AHB zbernice ktoré spolu so svojimi APB zbernicami obsluhujú väčšinu periférií typu SPI/I2C/UART atď, (aj dve APB zbernice ale len ako slave pre DMA - viď v ďalšom - všetky ostatné mastre k APB pristupujú len cez príslušné AHB) a "prepoje" - už spomenutý D2-to-D1 a D2-to-D3. Je vhodné si tu všimnúť DMA kontroléry. Majú po 8 kanálov a 2 porty smerom k matici, rovnako ako DMA jednotky v 'F7/'F4; na rozdiel od nich však jeden z portov (periférny) nie je priamo prepojený "skratkou" na príslušnú APB zbernicu, ale je vedený tiež maticou, s prístupom na všetky slave (vrátane oboch APB, ako bolo spomenuté). Ďalším rozdielom je "request router", v ktorom by malo byť možné voľnejšie presmerovávať požiadavky na prenos od jednotlivých periférií na jednotlivé kanály DMA (presné informácie zatiaľ chýbajú). Obe tieto zmeny prispievajú k vyššej flexibilite použitia DMA jednotiek (ktorá v 'F7/'F4 naráža na množstvo "natvrdo zapojených" obmedzení), zjavne za cenu väčšieho počtu tranzistorov a prepojov.

Matica D3 je nízkopríkonová a má okrem prepojov z D1 a D2 jediný samostatný master a to je "Basic" DMA (BDMA) jednotku. Ako slave má blok 64kB SRAM a 4kB zálohovanej SRAM, a AHB4 zbernicu ktorá spolu s APB4 zbernicou obsluhuje periférie ako RTC, low- power timery, LPUSART a iné.

"Prepoje" sú teda obojsmerné medzi všetkými tromi maticami s výnimkou smeru D3-to-Dx, takže jediný D3 master BDMA môže pristupovať len na slave v D3. Treba si pritom uvedomiť, že tieto "prepoje" (AHB zbernice) sú "pomalšie" - väčšina z nich môže ísť max. do rýchlosti 200MHz. Samozrejme, v každej matici nastáva proces arbitrácie medzi mastrami, ktorý vnáša latencie do prístupu k pripojeným slave aj keď nenastáva konflikt. Ak je z nejakého mastra pristupovaná periféria pripojená na inú zbernicu ktorá je slavom inej matice než v ktorej sa nachádza master, tento prístup prechádza oboma maticami plus prepojom medzi nimi, takže predstavuje určité spomalenie a záťaž pre všetky dotknuté zbernice a matice. Preto napríklad nie je vhodné, aby jednotka DMA1 (master v D2) zbytočne pristupovala na externú pamäť (trebárs SRAM) cez FMC (čo je slave v D1) - znamenalo by to cestu cez D2, prepoj D2-D1, a cestu cez D1; je vhodnejšie, ak si DMA1 rieši väčšinu pamäťových potrieb niektorou z lokálnych pamätí v D2, t.j. SRAM1-SRAM3.

Na takto hierarchicky zostavený obvod je teda vhodné nazerať ako na výkonný procesor s úzko pripojenými pamäťami (to predstavuje D1), a k nemu voľnejšie pripojenú sadu periférií (D2 a D3). Očakáva sa, že D1 rieši výpočtovo náročné úlohy (number crunching), kým väčšina riadiacich hard-real-time úloh sú riešené buď priamo perifériami (ktoré každá sama osebe predstavuje systém nemalej zložitosti), menšia časť z nich a väčšina presunu dát je riešená DMA jednotkami, a procesor nad nimi vlastne robí len dohľad prípadne dávkovo spracováva data.

Je to ešte o jednu úroveň vzdialenejšie modelu, ktorý zaviedli 8-bitové mcu. Tie mali všetky zdroje - procesorové jadro, pamäte aj periférie - úzko zviazané a prísne synchrónne, čo umožňovalo vývojárovi mať veľmi presnú kontrolu nad časovaním; na druhej strane výpočtový výkon bol častokrát nedostatočný pre náročnejšie aplikácie. 32-bitové mcu - vlastne SoC - priniesli o rád vyšší výpočtový výkon; na výmenu za to sú však jednotlivé moduly zviazané voľnejšie cez sústavu zberníc a signálov, niekedy aj v rôznych časovacích doménach, kde dosiahnutie presného časovania procesov riadených priamo z procesora je obtiažne ba až nemožné. STM32H7 posúva tento rozpor ešte o stupeň ďalej.

Cena, dostupnosť

Jedná sa samozrejme o predbežné oznámenie, a obvody STM32H743 existujú ešte len ako vzorky, preto o cene a dostupnosti sa zatiaľ nedá hovoriť. Tlačová správa uvádza, že obvod bude vyrábaný v Q2 2017, a predbežná cena najnižšieho modelu s 1MB FLASH v 100-pinovom puzdre je $8.17 pri 10k.

Z doterajších skúseností je pravdepodobné, že niekedy v druhej polovici budúceho roku sa objavia prvé kusy samotného obvodu ako aj podporné kity typu DISCOVERY či Nucleo a maloobchodná cena v bude pravdepodobne bližšie k $20. Pri takto zložitom obvode však treba rátať aj s obdobím počiatočných potiaží v zvládnutí softwaru a určitým množstvom errat, ako to k tak príšerne zložitým obvodom nevyhnutne patrí.

Odkazy

- STM32H7 Series homepage

- DB2923: 32-bit ARM® Cortex®-M7 400MHz MCU, up to 2MB Flash, 1MB RAM, 46 communication and analog interfaces, LCD-TFT & JPEG Codec

Táto novinka je z mikroZONE

( http://www.mikrozone.sk/news.php?extend.1203 )